# EE 505

Lecture 18

Architectural Performance Comparisons

ADC Design

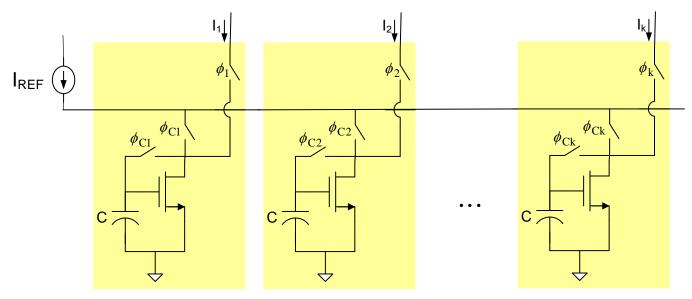

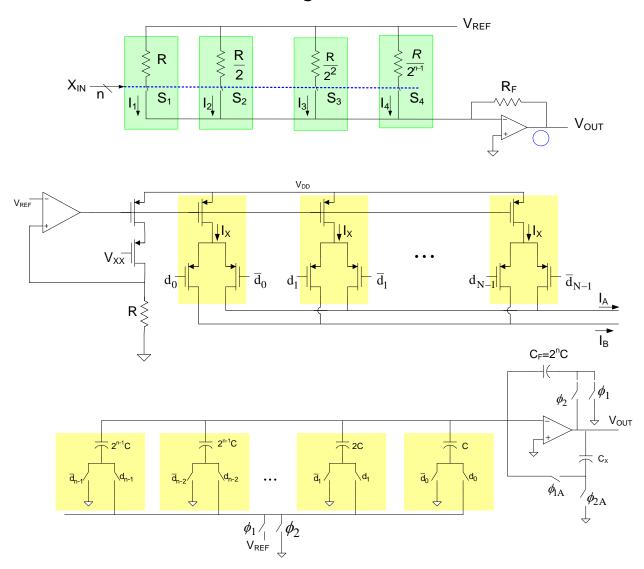

## Dynamic Current Source Matching

- Correct charge is stored on C to make all currents equal to I<sub>REF</sub>

- Does not require matching of transistors or capacitors

- Requires refreshing to keep charge on C

- Form of self-calibration

- Calibrates current sources one at a time

- Current source unavailable for use while calibrating

- Can be directly used in DACs (thermometer or binary coded)

- Still use steering rather than switching in DAC

Often termed "Current Copier" or "Current Replication" circuit

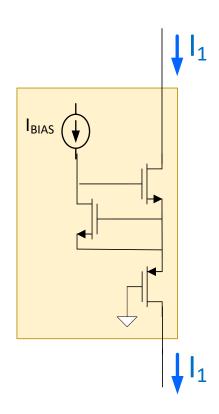

## Floating Current Source

## Floating Current Copier

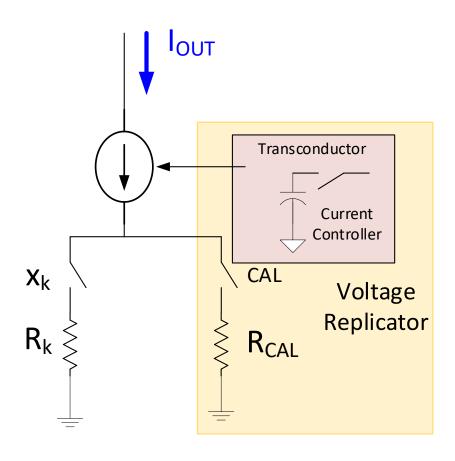

#### Another Dynamic Current Source Matching Structure

Floating Current Source

Voltage Copier

Eliminates need to remove current source from circuit during cal

## Noise in DACs

Resistors and transistors contribute device noise but what about charge redistribution DACs?

## Noise in DACs

Resistors and transistors contribute device noise but what about charge redistribution DACs?

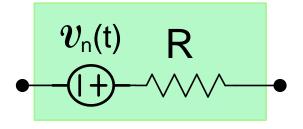

#### Noise in resistors:

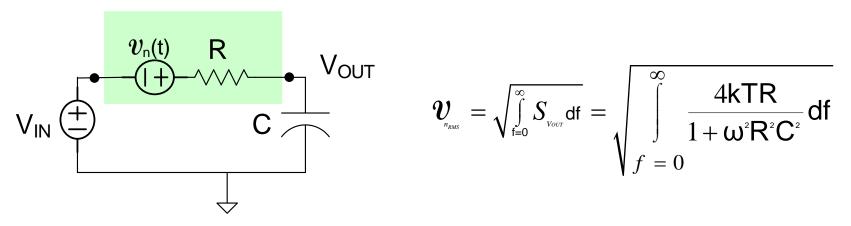

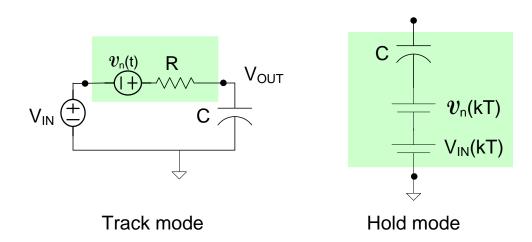

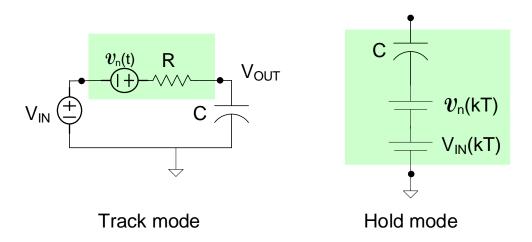

Noise spectral density of  $v_{\rm n}({\rm t})$  at all frequencies S=4kTR

$$S = 4kTR$$

This is white noise!

k: Boltzmann's Constant

T: Temperature in Kelvin

$k=1.38064852 \times 10^{-23} \text{ m}^2 \text{ kg s}^{-2} \text{ K}^{-1}$

At 300K,  $kT=4.14 \times 10^{-21}$

## Noise in DACs

Resistors and transistors contribute device noise but what about charge redistribution DACs?

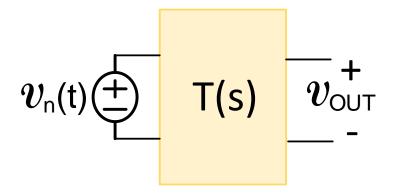

#### Noise in linear circuits:

Due to any noise voltage source:

$$S_{_{\scriptscriptstyle VOUT}} = S_{_{\scriptscriptstyle V_{\scriptscriptstyle n}}} \left| T \left( j \omega

ight) \right|^2$$

$$oldsymbol{v}_{\scriptscriptstyle OUT_{\scriptscriptstyle RMS}} = \sqrt{\int\limits_{\scriptscriptstyle {

m f=0}}^{\infty} S_{\scriptscriptstyle {\scriptscriptstyle VOUT}}} {

m d} {

m f} = \sqrt{\int\limits_{\scriptscriptstyle {\scriptscriptstyle T}}^{\infty} \left| S_{\scriptscriptstyle {\scriptscriptstyle V_{\scriptscriptstyle n}}} \left| T\left(j\omega

ight)

ight|^{\scriptscriptstyle 2}} {

m d} {

m f}$$

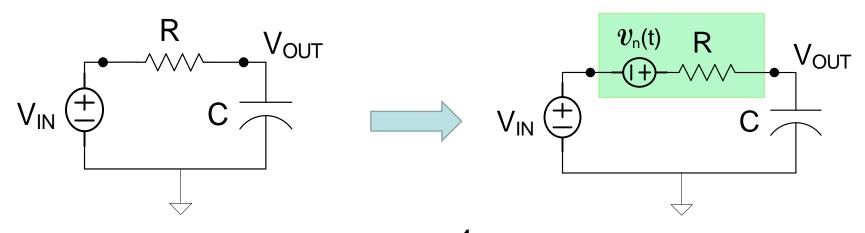

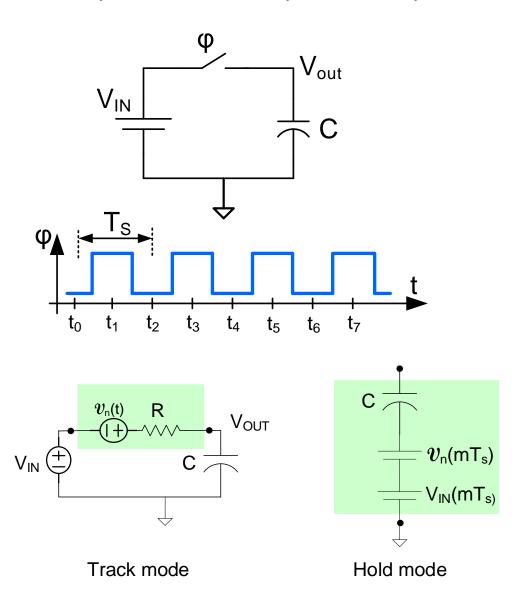

#### Example: First-Order RC Network

$$\mathsf{T}(s) = \frac{1}{1 + \mathsf{RCs}}$$

$$S_{vout} = 4kTR \left( \frac{1}{1 + (RC\omega)^2} \right)$$

$$\mathbf{v}_{n_{RMS}} = \sqrt{\int_{f=0}^{\infty} S_{vout} df} = \sqrt{\int_{f=0}^{\infty} \frac{4kTR}{1 + \omega^{2}R^{2}C^{2}}} df$$

## **Useful Trig Identity:**

$$\mathbf{v}_{_{n_{\text{RMS}}}} = \sqrt{\int\limits_{\text{f=0}}^{\infty} S_{_{\text{VOUT}}} df} = \sqrt{\int\limits_{\text{f=0}}^{\infty} \frac{4kTR}{1 + \omega^2 R^2 C^2} df} = \sqrt{\frac{4kT}{RC^2}} \int\limits_{\text{f=0}}^{\infty} \frac{1}{\left(\frac{1}{RC}\right)^2 + \omega^2} df$$

$$\int_{x=0}^{\infty} \frac{1}{a^2 + x^2} \, dx = \frac{\pi}{2a}$$

If  $\omega = 2\pi \mathbf{f}$  this can be rewritten as

$$\int_{f=0}^{\infty} \frac{1}{b^2 + \omega^2} df = \frac{1}{4b}$$

Example: First-Order RC Network

From a standard change of variable with a trig identity, it follows that

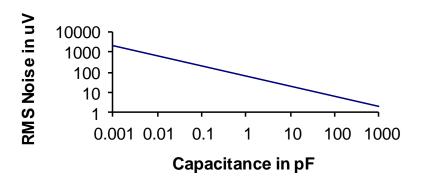

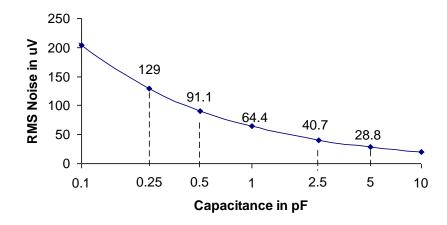

$$oldsymbol{v}_{\scriptscriptstyle n_{\scriptscriptstyle RMS}} = \sqrt{\int\limits_{\scriptscriptstyle \mathsf{f}=0}^{\infty} S_{\scriptscriptstyle \scriptscriptstyle VOUT}} \mathsf{df} = \sqrt{rac{\mathsf{kT}}{\mathsf{C}}}$$

- The continuous-time noise voltage has an RMS value that is independent of R

- Noise contributed by the resistor is dependent only upon the capacitor value C

- This is often referred to at kT/C noise and it can be decreased at a given T only by increasing C

"kT/C" Noise at T=300K

"kT/C" Noise at T=300K

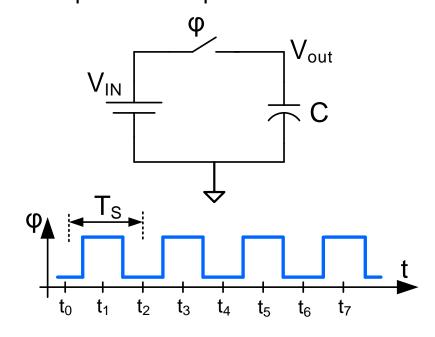

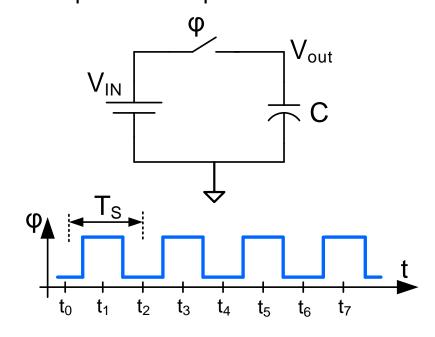

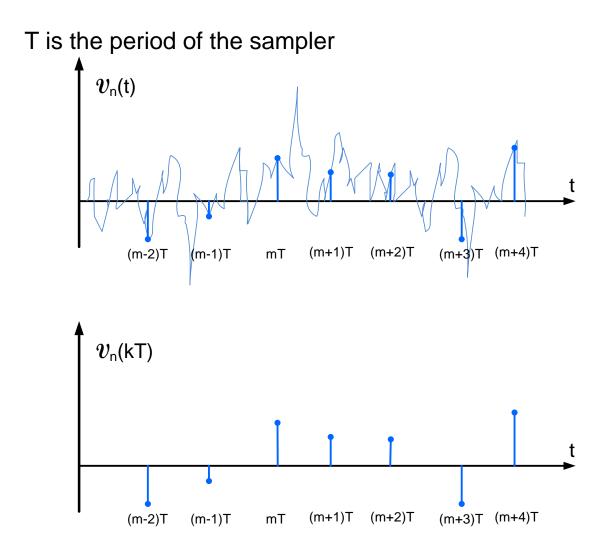

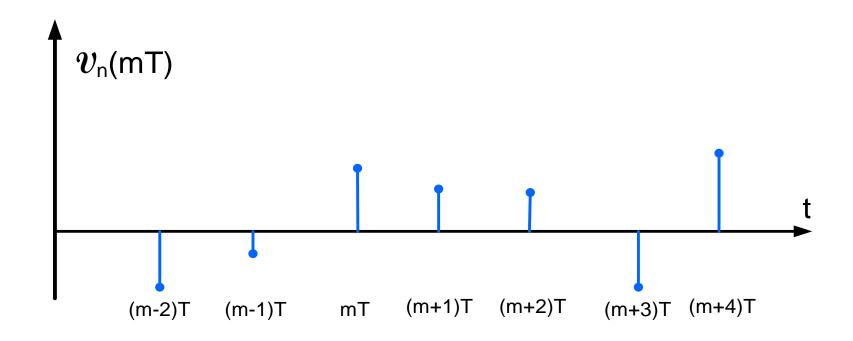

$v_{\rm n}({

m mT})$  is a discrete-time sequence obtained by sampling continuous-time noise waveform

#### Characterization of a noise sequence

$$\hat{\boldsymbol{v}}_{\scriptscriptstyle{\text{RMS}}} = E \left( \sqrt{\lim_{N \to \infty} \left( \frac{1}{N} \sum_{m=1}^{N} \boldsymbol{v}^{\scriptscriptstyle{2}} \left( \mathsf{mT} \right) \right)} \right) \underset{\scriptscriptstyle{N \, / \, \mathsf{arg}_{e}}}{\simeq} \sqrt{\frac{1}{N} \sum_{m=1}^{N} \boldsymbol{v}^{\scriptscriptstyle{2}} \left( \mathsf{mT} \right)}$$

**Theorem** If v(t) is a continuous-time zero-mean noise source and v(kT) is a sampled version of v(t) sampled at times T, 2T, .... then the RMS value of the continuous-time waveform is the same as that of the sampled version of the waveform. This can be expressed as  $v(t) = \hat{v}(t)$

**Theorem** If v(t) is a continuous-time zero-mean noise signal and v(t) is a sampled version of v(t) sampled at times T, 2T, .... then the standard deviation of the random variable v(t), denoted as  $\sigma_{v}$  satisfies the expression  $\sigma_{v} = v(t)$

$$v_{_{n_{RMS}}} = \sqrt{rac{\mathsf{kT}}{\mathsf{C}}}$$

k: Boltzmann's constantT: temperature in Kelvin

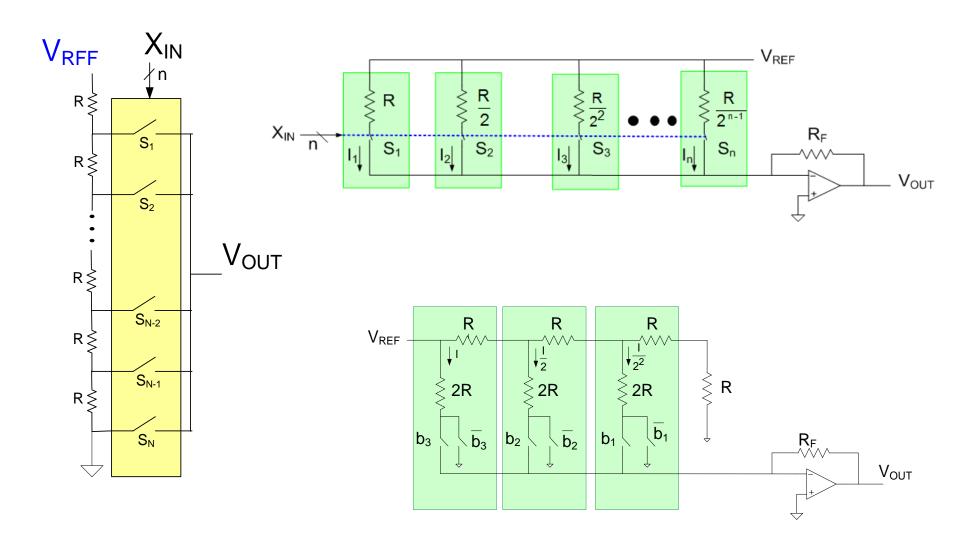

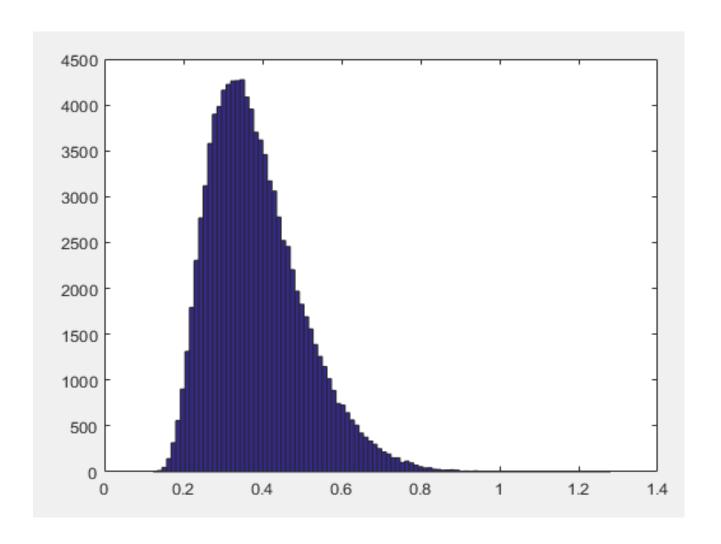

### **Architectural Performance Characterizations**

For the same total resistor area and the same resolution, how do these structures compare from a statistical characterization viewpoint?

For the same total area and the same resolution, how do these structures compare from a statistical characterization viewpoint?

#### Simulation environment:

Resolution = 10

$A_{\rho R} = 0.02 \mu m$

Rnom = 1000

Area Unit Resistor =  $2\mu m^2$

Resistor Sigma= 14.1421

INLtarget = 0.5000 LSB

Yield: Must meet INL target

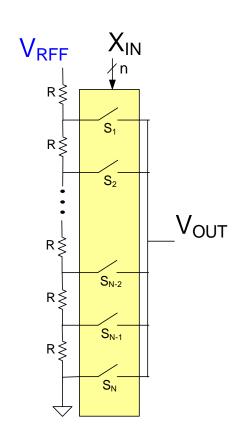

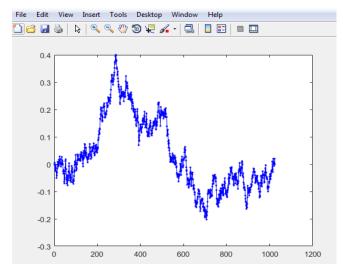

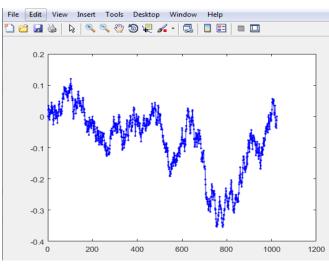

## INL<sub>k</sub> for four random implementations

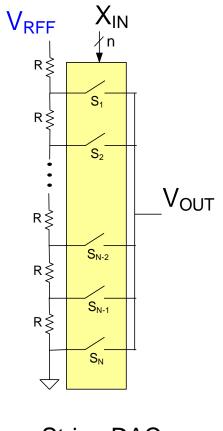

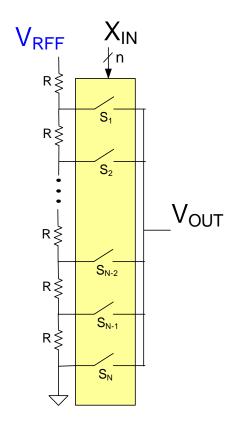

String DAC

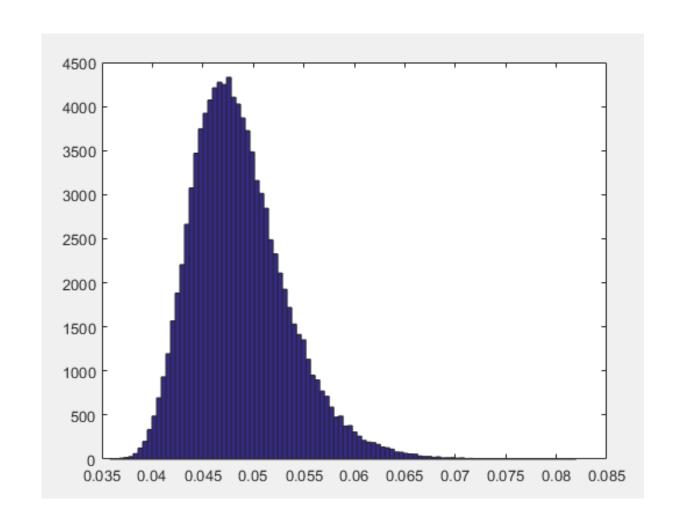

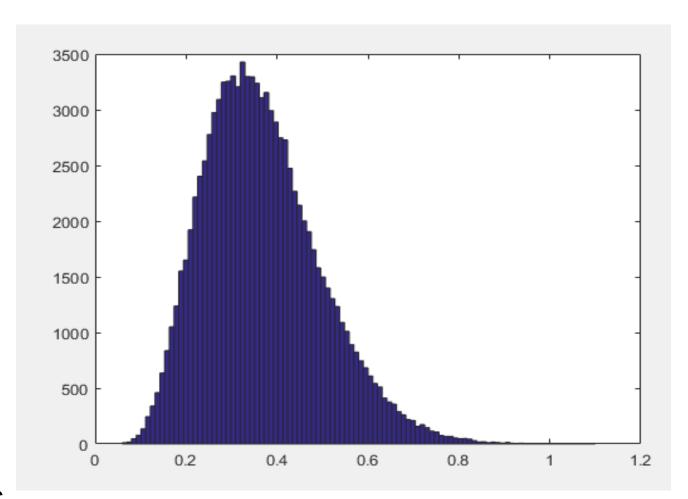

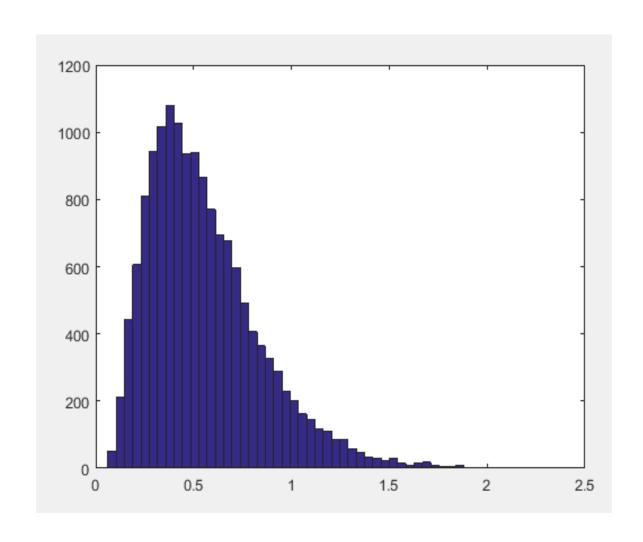

## INL histogram for 100,000 random implementations

String DAC

INL<sub>kMAX</sub> histogram for 100,000 random implementations

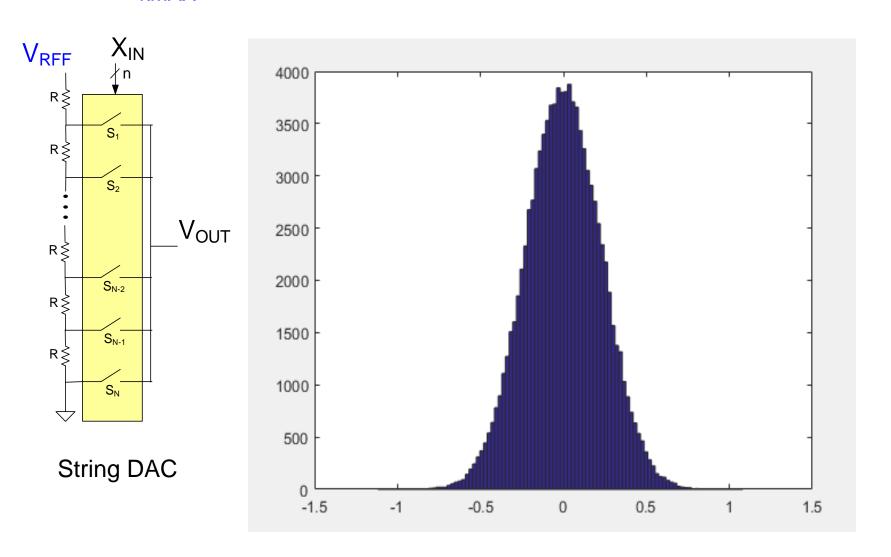

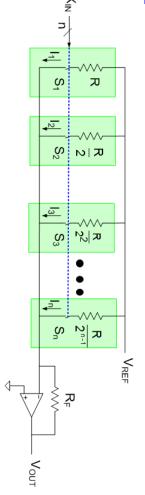

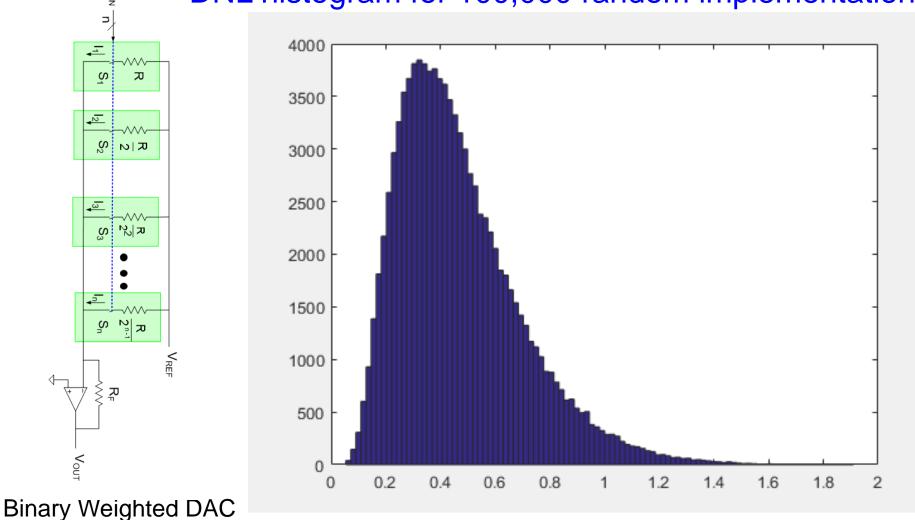

## DNL histogram for 100,000 random implementations

String DAC

String DAC

#### **Summary**

Resolution = 10

$A_{oR} = 0.02 \mu m$

$R_{nom} = 1000$

Area Unit Resistor =  $2\mu m^2$

Resistor Sigma= 14.1421

$INL_{mean} = 0.385 LSB$

$INL_{sigma} = 0.118 LSB$

$DNL_{mean} = 0.049 LSB$

$DNL_{sigma} = 0.0047 LSB$

Yield (%) = 84.0

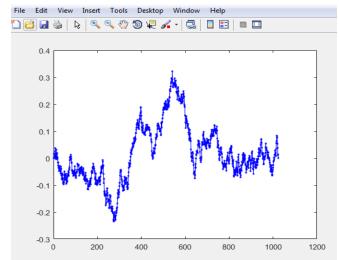

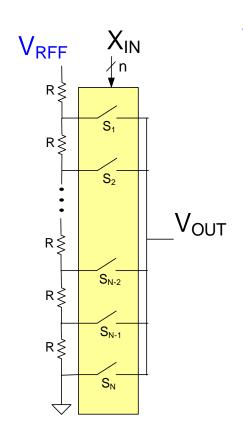

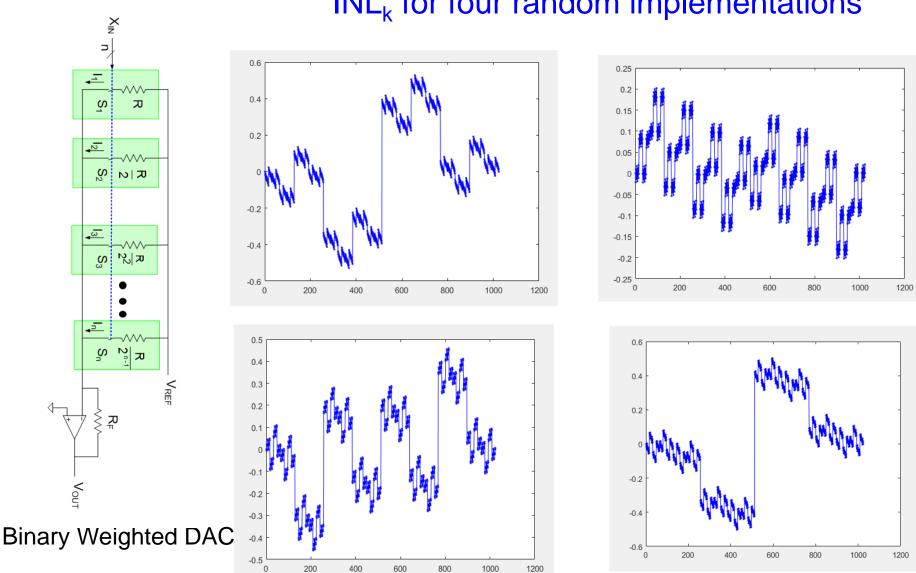

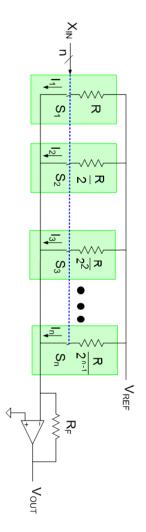

INL<sub>k</sub> for four random implementations

INL histogram for 100,000 random implementations

Binary Weighted DAC

INL<sub>kMAX</sub> histogram for 100,000 random implementations

Binary Weighted DAC

Binary Weighted DAC

Summary

Resolution = 10

$A_{\rho R} = 0.02 \mu m$

$R_{nom} = 1000$

Area unit resistor=2µm<sup>2</sup>

Resistor Sigma= 14.1421

$INL_{mean} = 0.367LSB$

$INL_{sigma} = 0.128 LSB$

$INL_{kmax\_mean} = 0.00013 LSB$

$INL_{kmax\_sigma} = 0.226 LSB$

$DNL_{mean} = 0.470 LSB$

$DNL_{sigma} = 0.228 LSB$

$INL_{target} = 0.500 LSB$

Yield (%) = 84.9

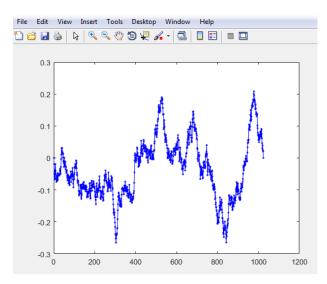

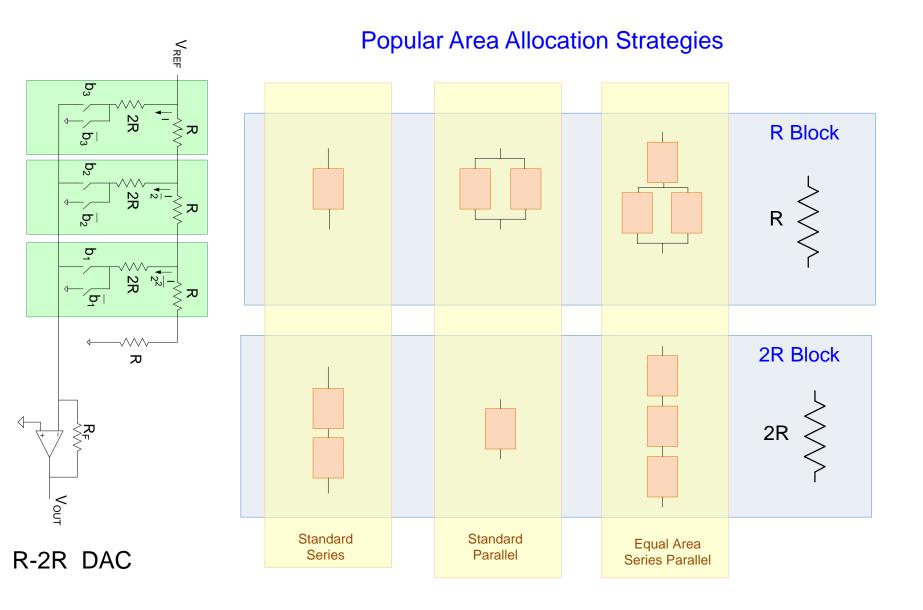

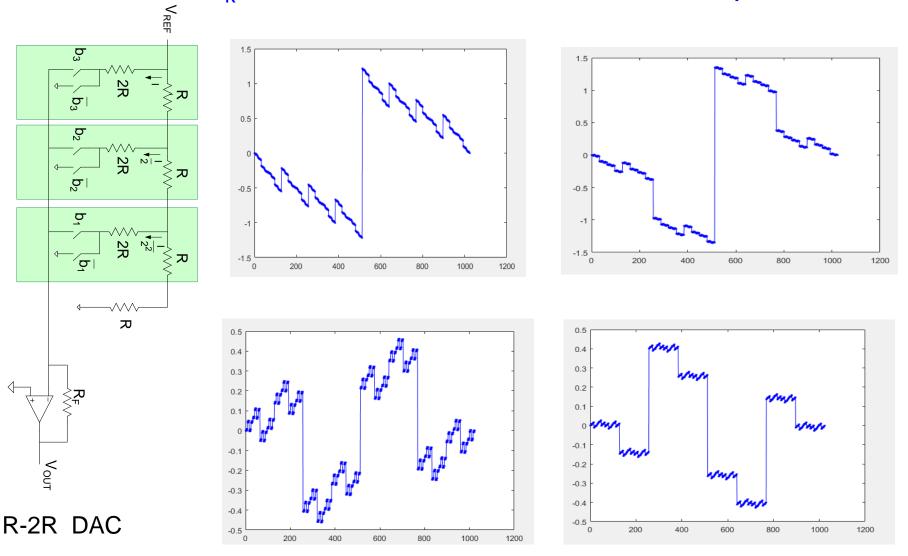

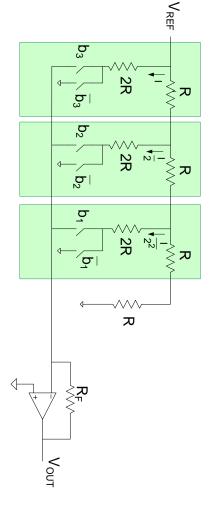

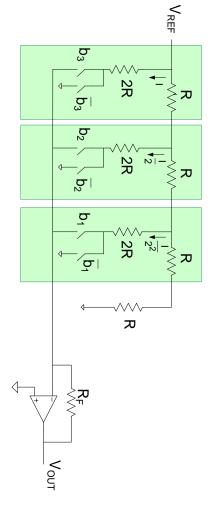

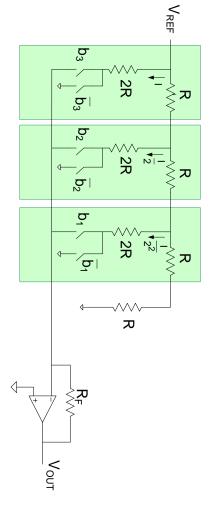

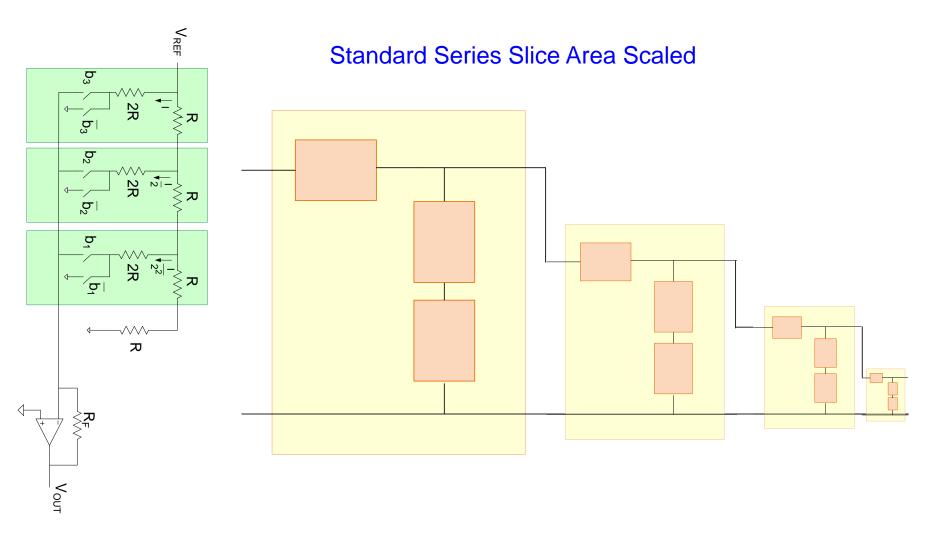

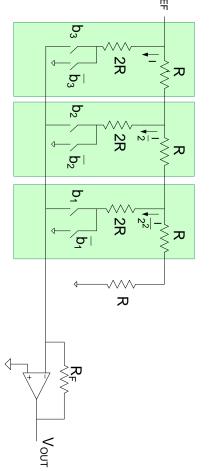

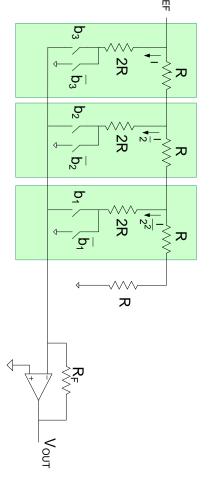

INL<sub>k</sub> for four random standard series implementations

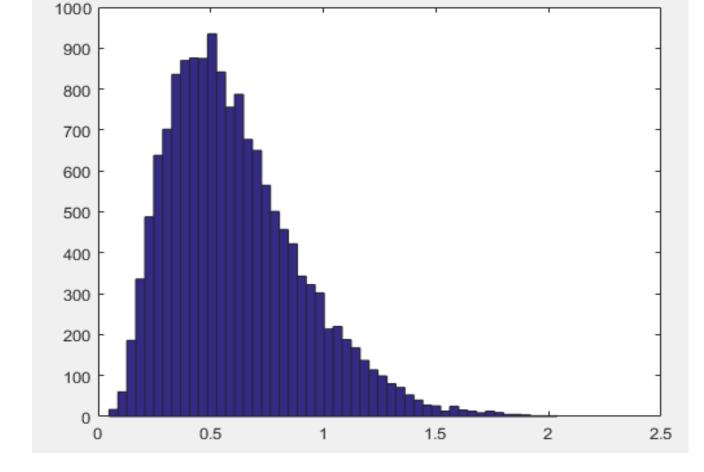

INL histogram for 15,000 random implementations Standard Series

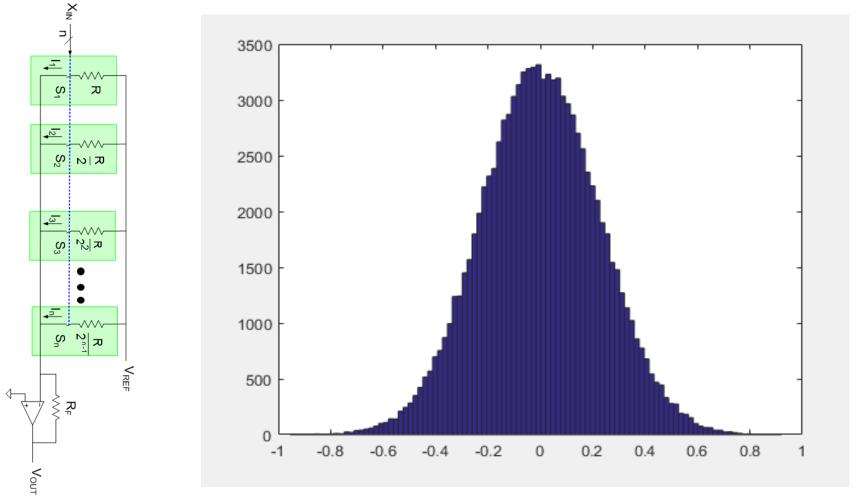

R-2R DAC

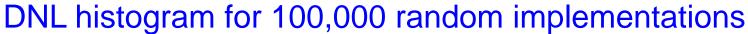

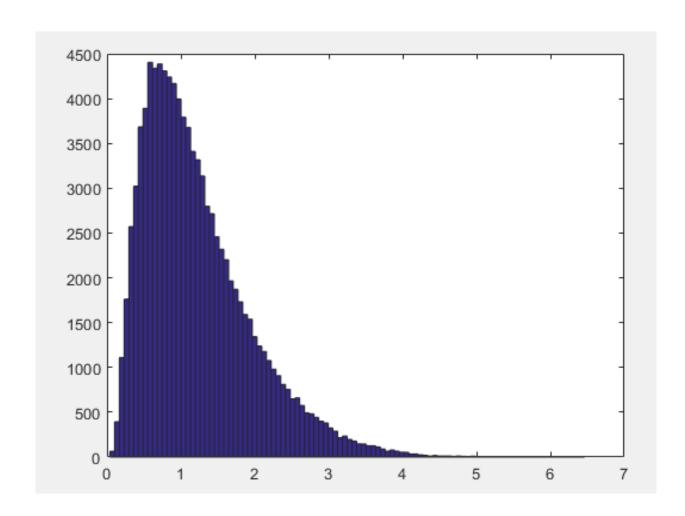

DNL histogram for 15,000 random implementations Standard Series

## Summary Standard Series

R-2R DAC

Resolution=10  $A_{pR} = 0.02 \, \mu m$ Rnom = 1000Base Res Area(um^2)=2 Res Sigma=14.1421  $INL_{mean} = 0.609 LSB$  $INL_{sigma} = 0.295 LSB$  $DNL_{mean} = 1.021 LSB$  $DNL_{sigma} = 0.610 LSB$  $INL_{kmax\_mean} = 0.00017 LSB$  $INL_{kmax sigm}a = 0.566 LSB$ Yield INL Bound=0.5 LSB Yield= 41.4%

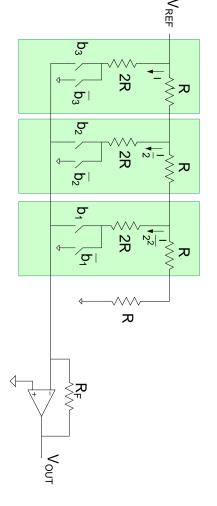

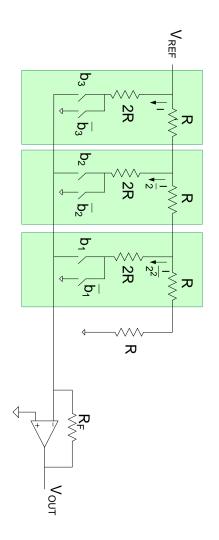

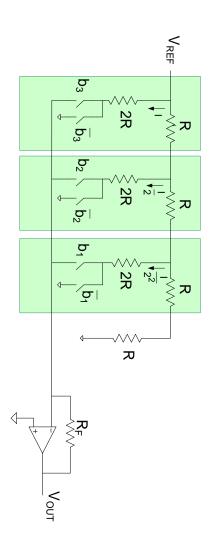

INL<sub>k</sub> for four random standard parallel implementations

1000

400

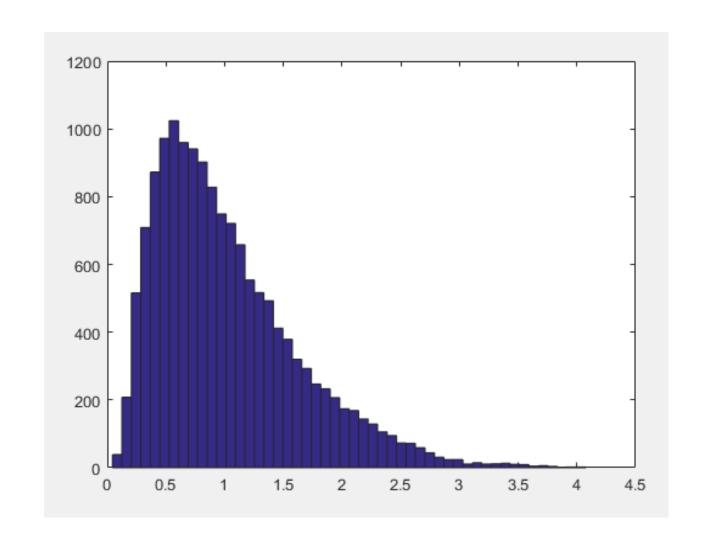

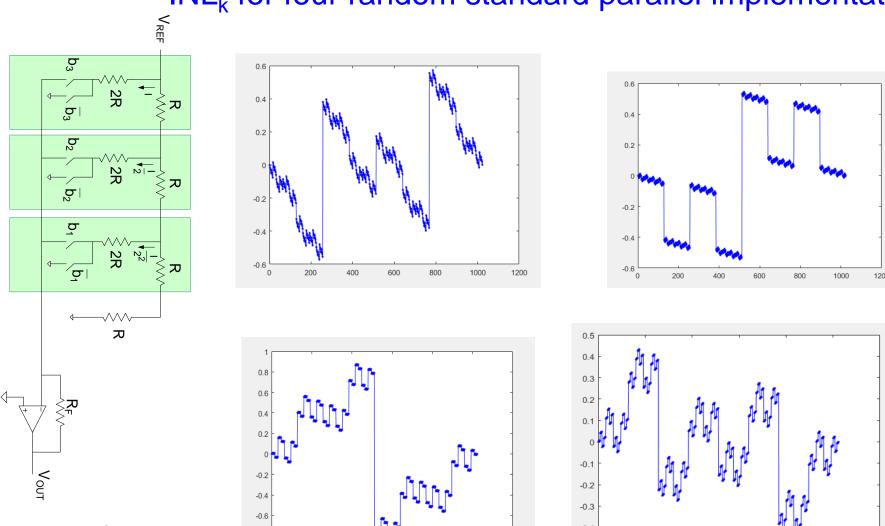

INL histogram for 100,000 random implementations Standard Parallel

DNL histogram for 100,000 random implementations Standard Parallel

R-2R DAC

### **Summary Standard Parallel**

```

Resolution = 10

A_{oR} = 0.02 \mu m

R_{nom} = 1000

Base Resistor Area(um^2) = 2

Resistor Sigma= 14.1421

INL_{mean} = 0.737 LSB

INL_{sigma} = 0.357 LSB

INL_{kmax\ mean} = 0.0045\ LSB

INL_{kmax\_sigma} = 0.680 LSB

DNL_{mean} = 1.225 LSB

DNL_{sigma} = 0.732 LSB

INL_{target} = 0.5 LS

Yield =28.5\%

```

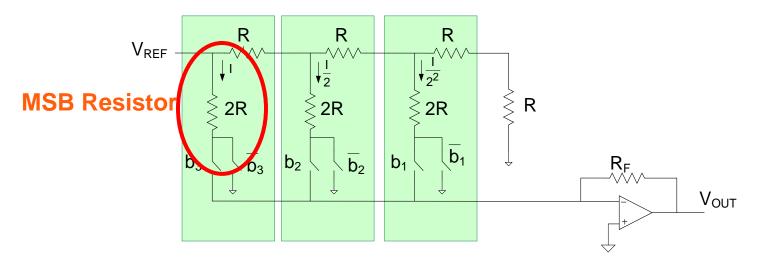

# Why is the Standard Series yield significantly larger than the Standard Parallel?

Standard Parallel

Yield =28.5%

Standard Series

Yield= 41.4%

Each bit slice has the same area

MSB resistor has higher percentage of area in Standard Series

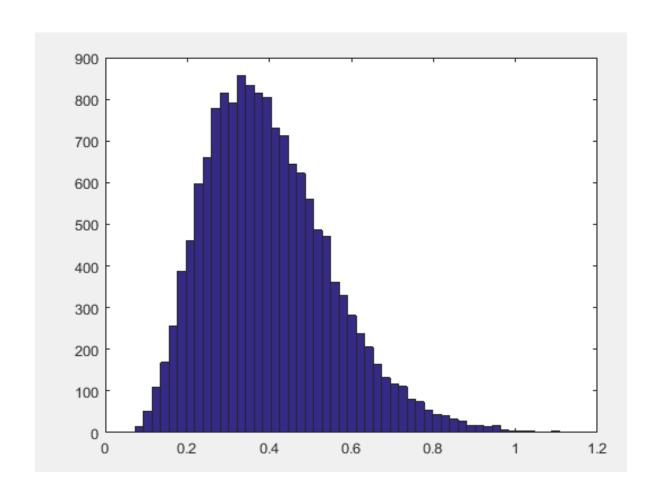

DNL histogram for 15,000 random implementations Standard Series Area Scaled Scaling Factor: 1.7

INL histogram for 15,000 random implementations Standard Series Area Scaled Scaling Factor: 1.7

R-2R DAC

Resolution = 10

$A_{pR} = 0.02 \mu m$

$R_{nom} = 1000$

Total Area 2048 µm<sup>2</sup>

Resistor Sigma= 14.1421

$INL_{target} = 0.5 LSB$

Yield = 28.5%

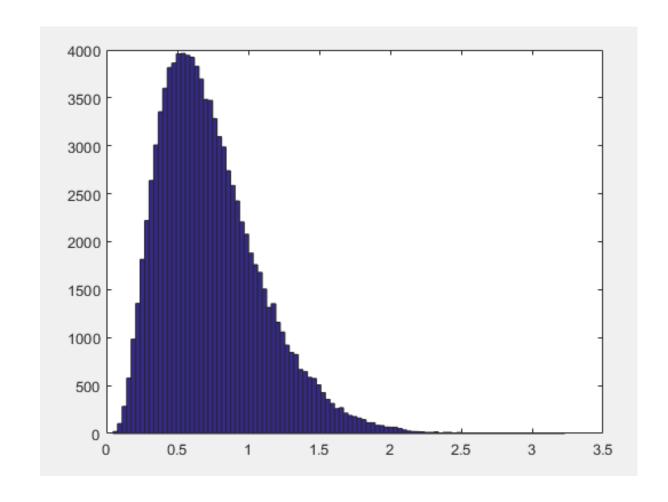

| Architecture                      | INL(LSB) |       | DNL(LSB) |        | INL   |

|-----------------------------------|----------|-------|----------|--------|-------|

|                                   | Mean     | Sigma | Mean     | Sigma  | Yield |

| String                            | 0.385    | 0.118 | 0.049    | 0.0047 | 84.0  |

| Binary Weighted                   | 0.367    | 0.128 | 0.470    | 0.228  | 84.9  |

| R-2R Series                       | 0.609    | 0.295 | 1.021    | 0.610  | 41.4  |

| R-2R Parallel                     | 0.737    | 0.357 | 1.225    | 0.732  | 28.5  |

| Slice Scaled (1.7)<br>Series R-2R | 0.399    | 0.153 | 0.556    | 0.286  | 76.4  |

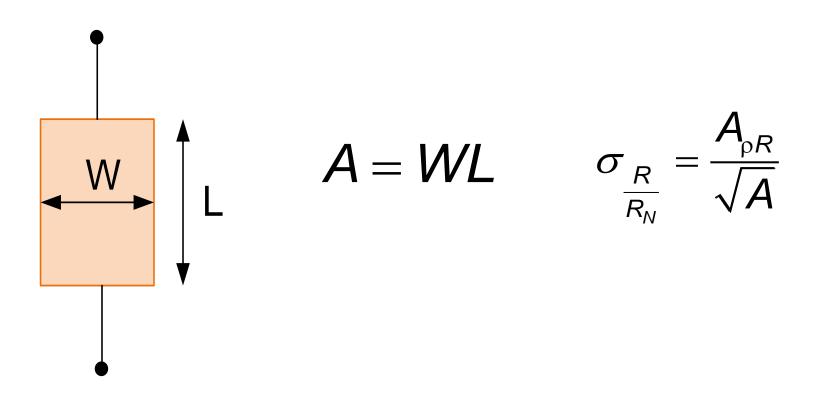

### Calibration of DACs

- The area required to get acceptable performance of a DAC is often too large to be practical

- Large DAC area invariably increased power dissipation

- Large DAC area invariably limits speed of a DAC

- Calibration is often used to improve the linearity of a DAC

- Calibration requires area overhead but it is often less than the area overhead that is required to improve yield using area alone

$$\sigma_{\frac{X}{X_N}} = \frac{A_X}{\sqrt{A}}$$

Benefits of using calibration are limited to the inherent noise in a DAC and calibration does not improve random noise (but can reduce quantization noise)

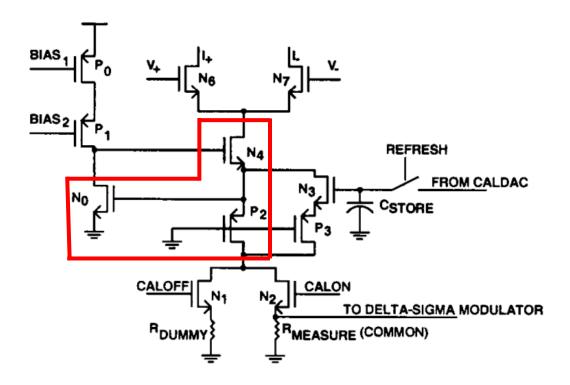

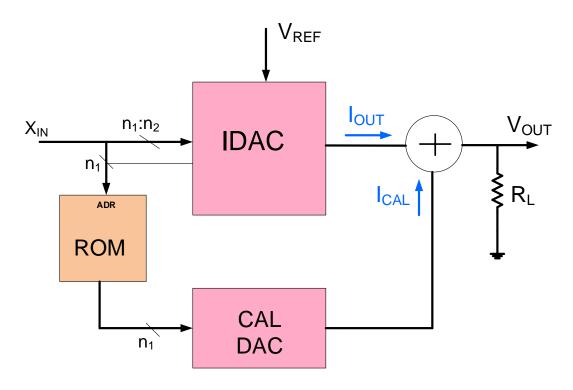

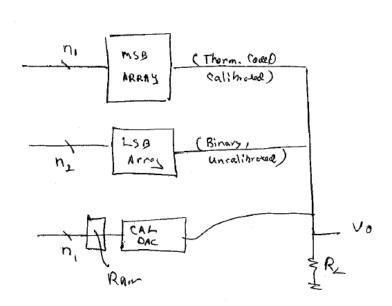

### Calibration of DACs

- If CAL DAC is driven by appropriate information in RAM, it can correct for nonlinearities in IDAC

- Resolution of CAL DAC can be small if IDAC is modestly linear

- Code in ROM can be programmed at test or during production

actual output of IDAC of then

add approp. Output from CALDAC

to obtain desired current

Dramotic Reduction Potential in Area for Higher-Resolution DACS

Higher-resolution DACs make extensive use of calibration or self-calibration

- Calibration corrects for nonlinearities (either discontinuities or smooth nonlinearities)

- Better high frequency performance

- Smaller die area

- Lower power dissipation

- Often more practical to calibrate for combined effects of all nonlinearities rather than correct the source of individual nonlinearities

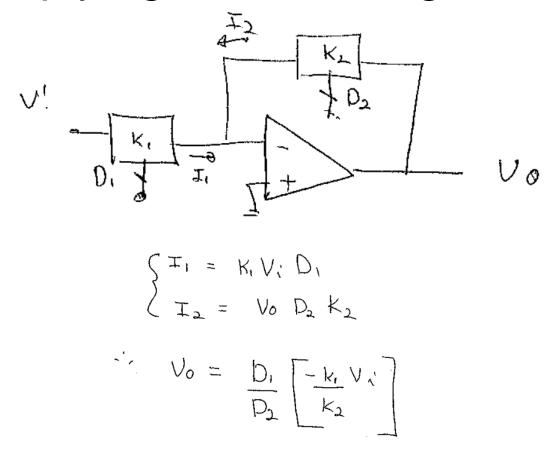

### Recall the MDAC

## Dividing DACs

V:

$$R$$

$I_2 = V_0 D k$

$V_1' = -I_2 R$

$V_2' = -V_0 D k R$

$V_3 = -V_0 D k R$

$V_4 = -V_0 D k R$

$V_5 = -V_0 D k R$

$V_6 = +V_1' \left(\frac{1}{D}\right) \left(\frac{1}{KR}\right)$

Could rall this  $D D A C$

## Multiplying and Dividing DACs

Can create various nonlinear relationships with MDACs and Op Amps

## ADC Design

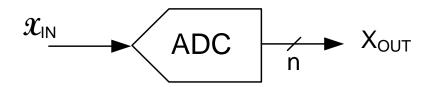

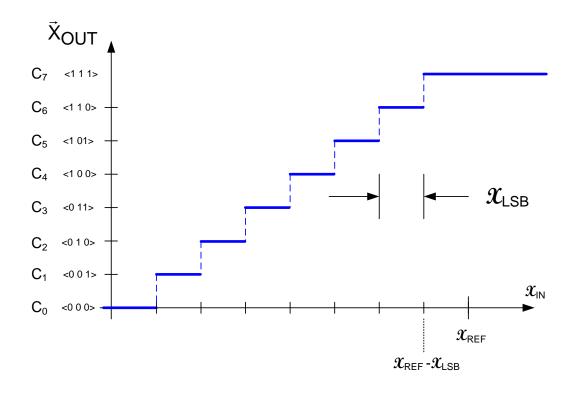

# Analog to Digital Converters

# Analog to Digital Converters

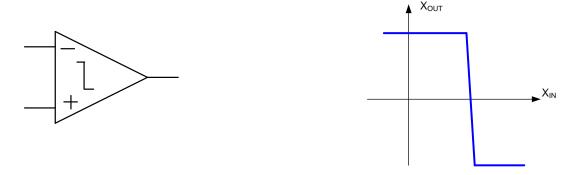

The conversion from analog to digital in ALL ADCs is done with comparators

ADC design is primarily involved with designing comparators and embedding these into circuits that are robust to nonideal effects

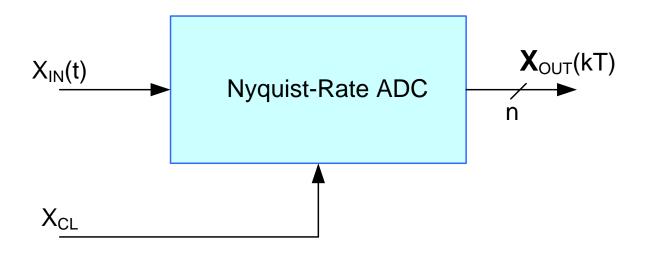

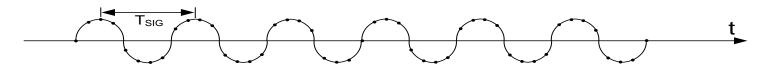

# Nyquist Rate

# Nyquist Rate

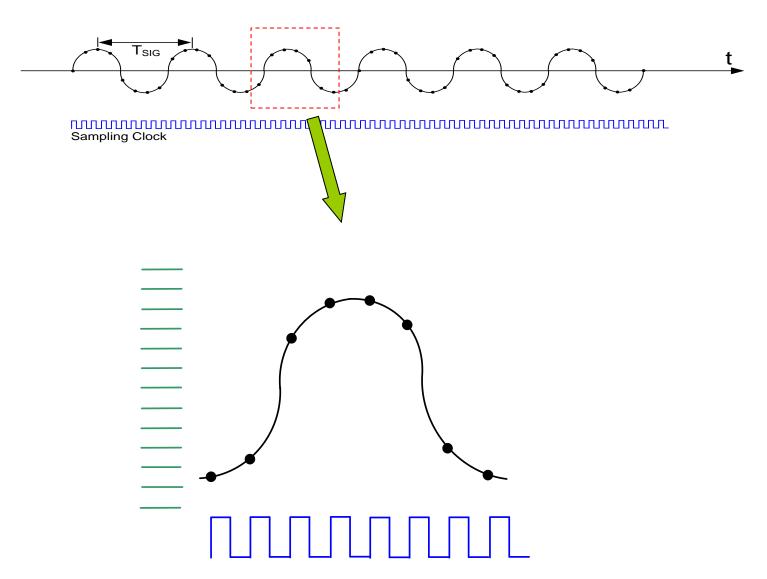

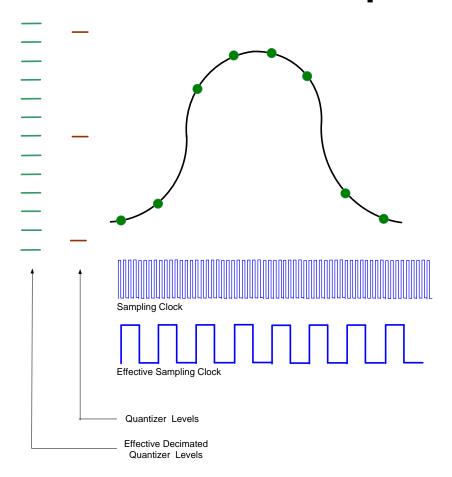

## Over-Sampled

Over-sampling ratios of 128:1 or 64:1 are common Dramatic reduction in quantization noise effects Limited to relatively low frequencies

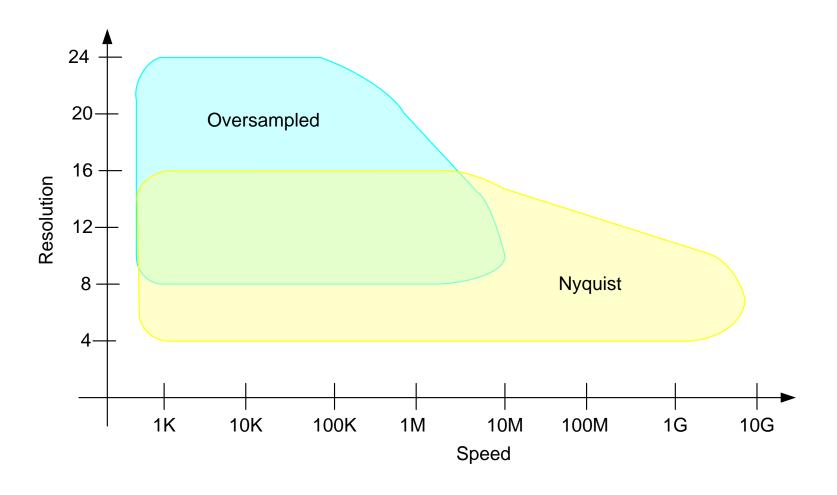

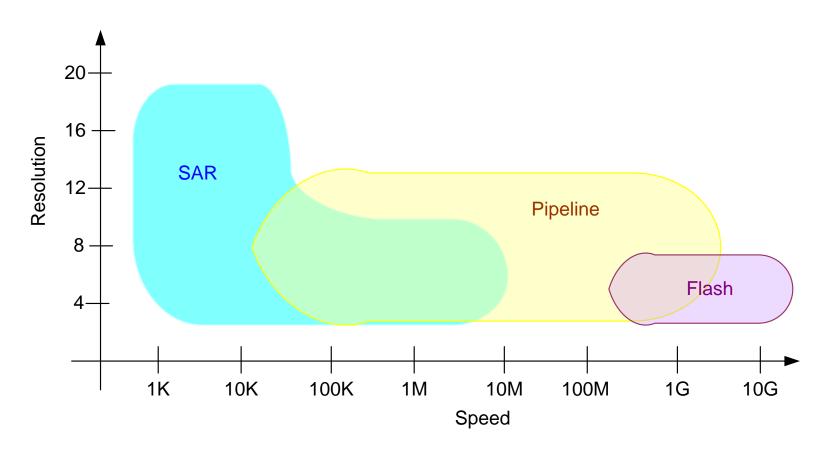

# Data Converter Type Chart

# **ADC Types**

### **Nyquist Rate**

- Flash

- Pipeline

- Two-Step Flash

- Multi-Step Flash

- Cyclic (algorithmic)

- Successive Approximation

- Folded

- Dual Slope

### **Over-Sampled**

- Single-bit

- Multi-bit

- First-order

- Higher-order

- Continuous-time

# Nyqyist Rate Usage Structures

Flash is the least used as a stand-alone structure but widely used as a subcomponent in SAR and Pipelined Structures

# **ADC Types**

### **Nyquist Rate**

- Flash

- Pipeline

- Two-Step Flash

- Multi-Step Flash

- Cyclic (algorithmic)

- Successive Approximation

- Folded

- Dual Slope

### **Over-Sampled**

- Single-bit

- Multi-bit

- First-order

- Higher-order

- Continuous-time

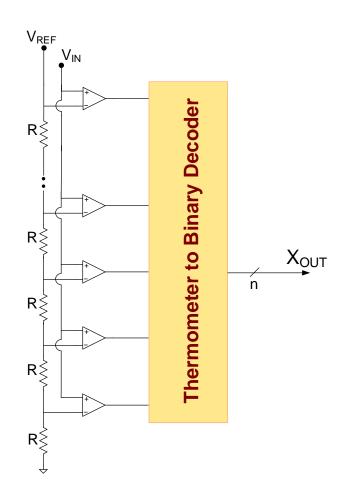

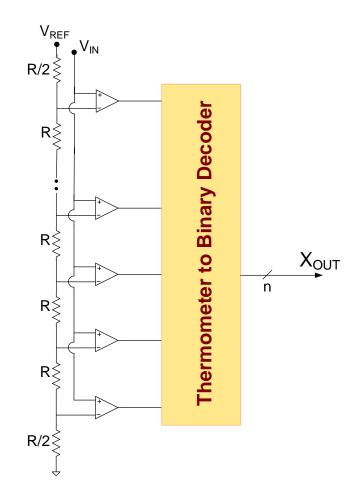

All have comparable conversion rates

Basic approach in all is very similar

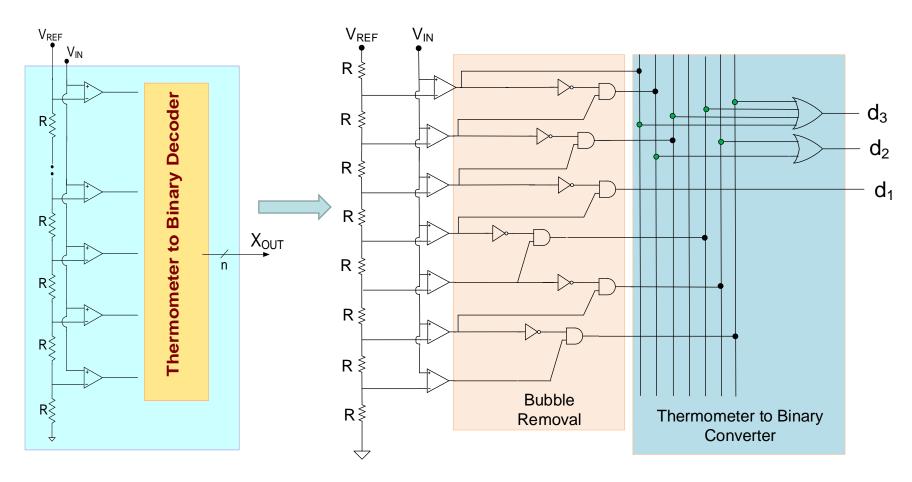

Basic structure has thermometer code at output

#### Performance Issues:

- + Very fast

- + Simple architecture

- + Instantaneous output

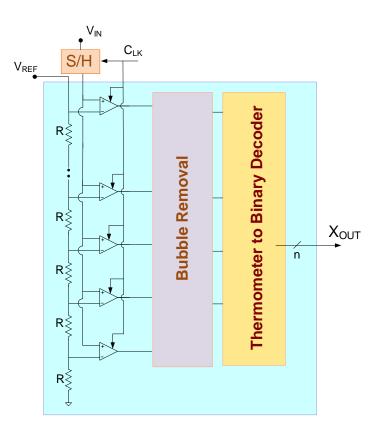

- → Bubble vulnerability

- Input change during conversion

- Offset of comparators

- Number of components and area (for large n)

- Speed of comparators

- Loading of  $V_{REF}$  and  $V_{IN}$

- Propagation of V<sub>IN</sub> and Kickback

- Power dissipation (for large n)

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

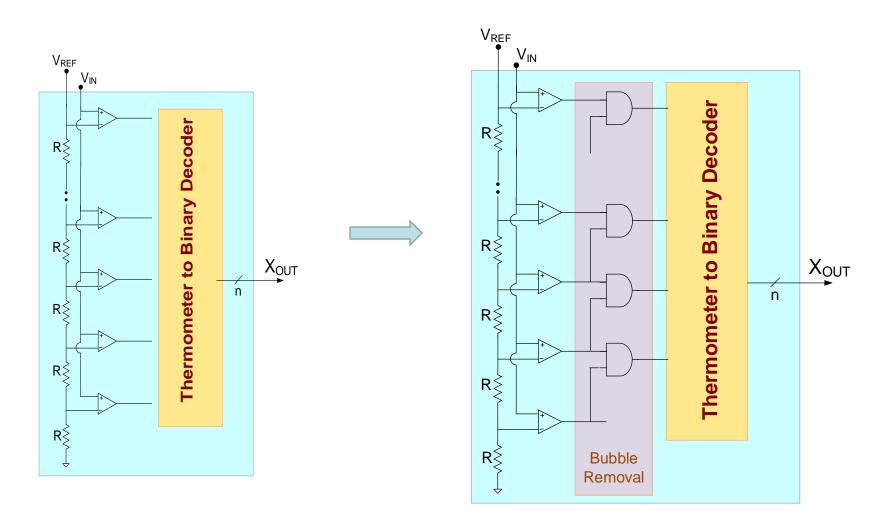

**Bubble Removal Approach**

Another Bubble Removal Approach

Stay Safe and Stay Healthy!

## End of Lecture 18